# SPECIFICATION

| Product     | 2.13inch e-Paper    |  |

|-------------|---------------------|--|

| Description | 2.13" E-PAPER, B/W  |  |

| Model Name  | 2.13inch e-Paper v2 |  |

| Date        | 2019/06/13          |  |

| Revision    | 2.0                 |  |

# **Table of Contents**

| 1. General Description                              | 4  |

|-----------------------------------------------------|----|

| 1.1 Overview                                        | 4  |

| 1.2 Feature                                         | 4  |

| 1.3 Mechanical Specification                        | 4  |

| 1.4 Mechanical Drawing of EPD module                | 5  |

| 1.5 Input/Output Terminals                          | 6  |

| 1.6 Reference Circuit                               | 8  |

| 2. Environmental                                    | 9  |

| 2.1 Handling, Safety and Environmental Requirements | 9  |

| 2.2 Reliability test                                | 11 |

| 3. Electrical Characteristics                       | 12 |

| 3.1 Absolute maximum rating                         | 12 |

| 3.2 Panel DC Characteristics                        | 12 |

| 3.3 Serial Peripheral Interface Timing              | 13 |

| 3.4 Power Consumption                               | 13 |

| 3.5 MCU Interface                                   | 14 |

| 3.6 Temperature sensor operation                    | 17 |

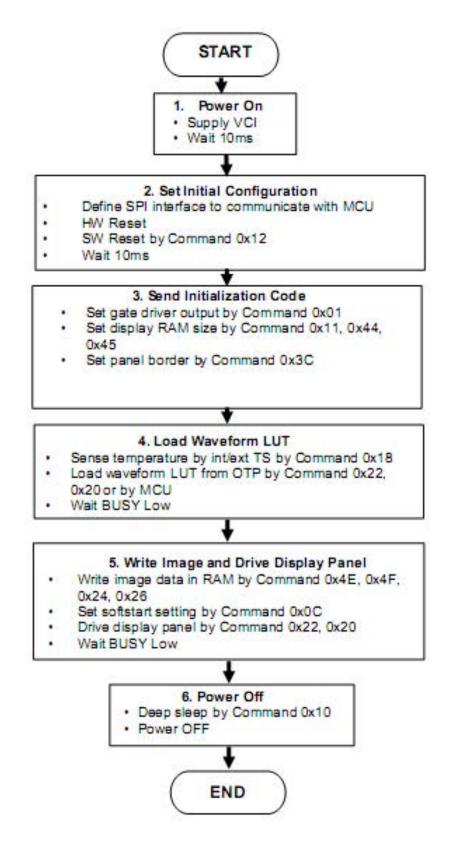

| 4. Typical Operating Sequence                       | 18 |

| 4.1 Normal Operation Flow                           | 18 |

| 5. Command Table                                    | 19 |

| 6. Optical characteristics                          |    |

| 6.1 Specifications                                  |    |

| 6.2 Definition of contrast ratio                    | 36 |

| 6.3 Reflection Ratio                                |    |

| 7. Point and line standard                          | 37 |

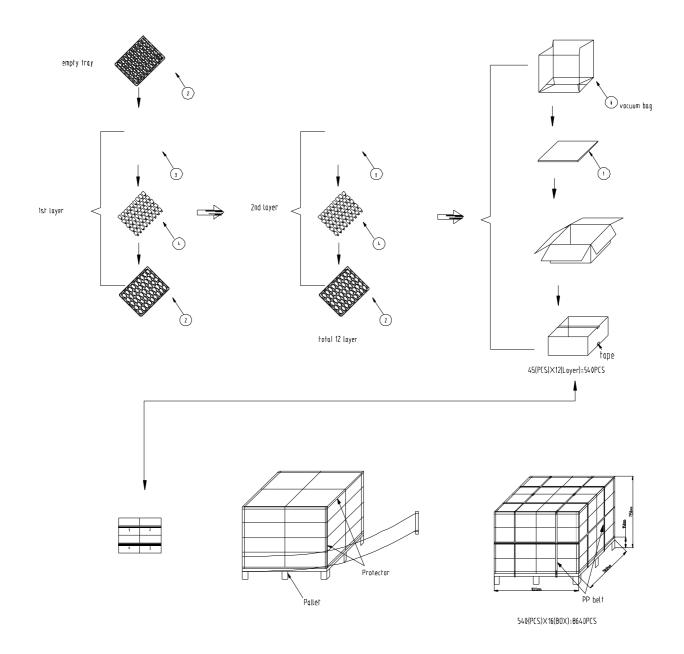

| 8. Packing                                          |    |

| 9. Precautions                                      |    |

# **Revision History**

| Rev. | <b>Issued Date</b> | Revised Contents                       |  |  |  |

|------|--------------------|----------------------------------------|--|--|--|

| 1.0  | June.26.2018       | Preliminary                            |  |  |  |

| 1.1  | Dec.07.2018        | ncreasing the Brand of components      |  |  |  |

| 2.0  | May.23.2019        | Update the reliability test conditions |  |  |  |

|      |                    |                                        |  |  |  |

|      |                    |                                        |  |  |  |

|      |                    |                                        |  |  |  |

|      |                    |                                        |  |  |  |

# **1. General Description**

## 1.1 Over View

2.13inch e-Paper is an Active Matrix Electrophoretic Display (AMEPD), with interface and a reference system design. The 2.13" active area contains 250×122 pixels, and has 1-bit B/W full display capabilities. An integrated circuit contains gate buffer, source buffer, interface, timing control logic, oscillator, DC-DC. SRAM.LUT, VCOM and border are supplied with each panel.

## **1.2 Features**

- Support partial refresh

- 250×122 pixels display

- High contrast

- High reflectance

- Ultra wide viewing angle

- Ultra low power consumption

- Pure reflective mode

- Bi-stable display

- Commercial temperature range

- Landscape, portrait modes

- Hard-coat antiglare display surface

- Ultra Low current deep sleep mode

- On chip display RAM

- Low voltage detect for supply voltage

- High voltage ready detect for driving voltage

- Internal temperature sensor

- 10-byte OTP space for module identification

- Waveform stored in On-chip OTP

- Serial peripheral interface available

- On-chip oscillator

- On-chip booster and regulator control for generating VCOM, Gate and Source driving voltage

• I2C signal master interface to read external temperature sensor/built-in temperature sensor

## **1.3 Mechanical Specifications**

| Parameter           | Specifications            | Unit  | Remark   |

|---------------------|---------------------------|-------|----------|

| Screen Size         | 2.13                      | Inch  |          |

| Display Resolution  | 122(H)×250(V)             | Pixel | Dpi: 130 |

| Active Area         | 23.7(H)×48.55(V)          | mm    |          |

| Pixel Pitch         | 0.1942×0.1943             | mm    |          |

| Pixel Configuration | Rectangle                 |       |          |

| Outline Dimension   | 29.2(H)×59.2 (V) ×1.05(D) | mm    |          |

| Weight              | 3.0±0.2                   | g     |          |

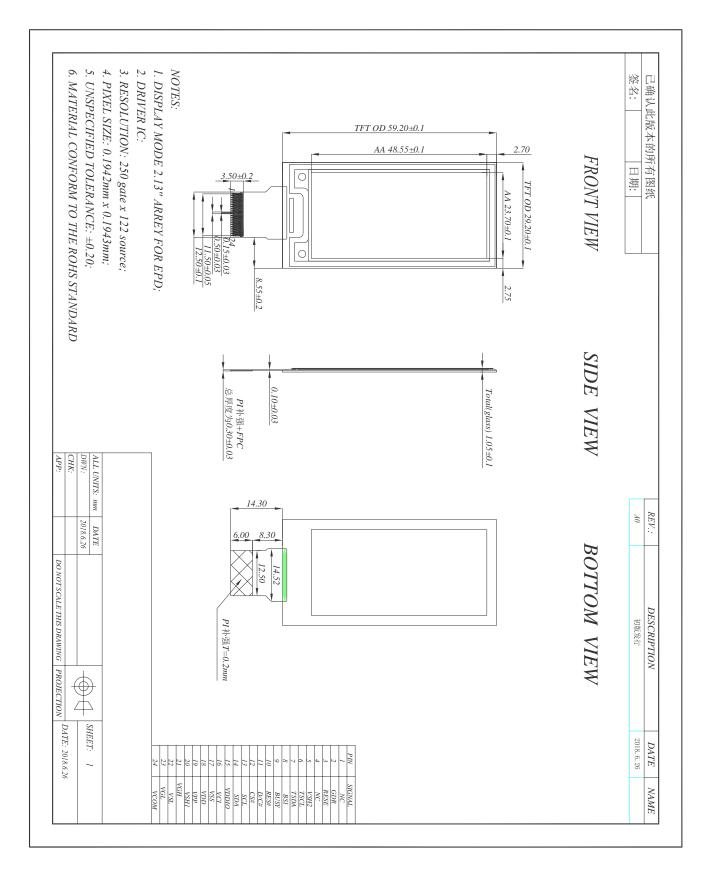

# **1.4 Mechanical Drawing of EPD module**

# 1.5 Input/Output Terminals

| Pin # | Single | ngle Description                                      |            |

|-------|--------|-------------------------------------------------------|------------|

| 1     | NC     | No connection and do not connect with other NC pins   | Keep Open  |

| 2     | GDR    | N-Channel MOSFET Gate Drive Control                   |            |

| 3     | RESE   | Current Sense Input for the Control Loop              |            |

| 4     | NC     | No connection and do not connect with other NC pins e | Keep Open  |

| 5     | VSH2   | This pin is Positive Source driving voltage           |            |

| 6     | TSCL   | I2C Interface to digital temperature sensor Clock pin |            |

| 7     | TSDA   | I2C Interface to digital temperature sensor Date pin  |            |

| 8     | BS1    | Bus selection pin                                     | Note 1.5-5 |

| 9     | BUSY   | Busy state output pin                                 | Note 1.5-4 |

| 10    | RES #  | Reset                                                 | Note 1.5-3 |

| 11    | D/C #  | Data /Command control pin                             | Note 1.5-2 |

| 12    | CS #   | Chip Select input pin                                 | Note 1.5-1 |

| 13    | SCL    | serial clock pin (SPI)                                |            |

| 14    | SDA    | serial data pin (SPI)                                 |            |

| 15    | VDDIO  | Power for interface logic pins                        |            |

| 16    | VCI    | Power Supply pin for the chip                         |            |

| 17    | VSS    | Ground                                                |            |

| 18    | VDD    | Core logic power pin                                  |            |

| 19    | VPP    | Power Supply for OTP Programming                      |            |

| 20    | VSH1   | This pin is Positive Source driving voltage           |            |

| 21    | VGH    | This pin is Positive Gate driving voltage             |            |

| 22    | VSL    | This pin is Negative Source driving voltage           |            |

| 23    | VGL    | This pin is Negative Gate driving voltage             |            |

| 24    | VCOM   | These pins are VCOM driving voltage                   |            |

Note 1.5-1: This pin (CS#) is the chip select input connecting to the MCU. The chip is enabled for MCU communication: only when CS# is pulled LOW.

Note 1.5-2: This pin (D/C#) is Data/Command control pin connecting to the MCU. When the pin is pulled HIGH, the data will be interpreted as data. When the pin is pulled LOW, the data will be interpreted as command.

Note 1.5-3: This pin (RES#) is reset signal input. The Reset is active low.

Note 1.5-4: This pin (BUSY) is Busy state output pin. When Busy is High the operation of chip should not be interrupted and any commands should not be issued to the module. The driver IC will put Busy pin High when the driver IC is working such as:

- Outputting display waveform; or

- Communicating with digital temperature sensor

Note 1.5-5: This pin (BS1) is for 3-line SPI or 4-line SPI selection. When it is "Low", 4-line SPI is selected. When it is "High", 3-line SPI (9 bits SPI) is selected.

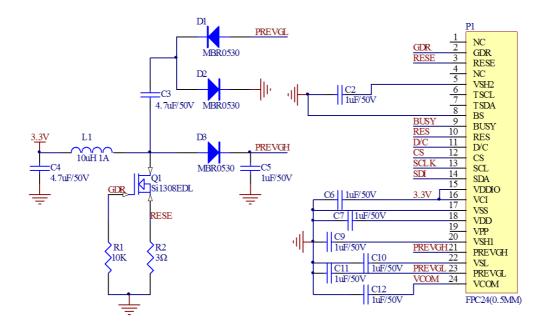

# **1.6 Reference Circuit**

#### Note :

- 1. Inductor L1 is wire-wound inductor. There are no special requirements for other parameters.

- 2. Suggests using Si1304BDL or Si1308EDL TUBE MOS (Q1) , otherwise it may affect the normal boost of the circuit.

- 3. The default circuit is 4-wire SPI. If the user wants to use 3-wire SPI.

- 4. Default voltage value of all capacitors is 50V.

# 2. Environmental

## 2.1 HANDLING, SAFETYAND ENVIROMENTAL REQUIREMENTS

#### WARNING

The display glass may break when it is dropped or bumped on a hard surface. Handle with care. Should the display break, do not touch the electrophoretic material. In case of contact with electrophoretic material, wash with water and soap.

## CAUTION

The display module should not be exposed to harmful gases, such as acid and alkali gases, which corrode electronic components.

Disassembling the display module can cause permanent damage and invalidate the warranty agreements.

IPA solvent can only be applied on active area and the back of a glass. For the rest part, it is not allowed.

Observe general precautions that are common to handling delicate electronic components. The glass can break and front surfaces can easily be damaged. Moreover the display is sensitive to static electricity and other rough environmental conditions.

#### Mounting Precautions

(1) It's recommended that you consider the mounting structure so that uneven force (ex. Twisted stress) is not applied to the module.

(2) It`s recommended that you attach a transparent protective plate to the surface in order to protect the EPD. Transparent protective plate should have sufficient strength in order to resist external force.

(3) You should adopt radiation structure to satisfy the temperature specification.

(4) Acetic acid type and chlorine type materials for the cover case are not desirable because the former generates corrosive gas of attacking the PS at high temperature and the latter causes circuit break by electro-chemical reaction.

(5) Do not touch, push or rub the exposed PS with glass, tweezers or anything harder than HB pencil lead. And please do not rub with dust clothes with chemical treatment. Do not touch the surface of PS for bare hand or greasy cloth. (Some cosmetics deteriorate the PS)

(6) When the surface becomes dusty, please wipe gently with absorbent cotton or other soft materials like chamois soaks with petroleum benzene. Normal-hexane is recommended for cleaning the adhesives used to attach the PS. Do not use acetone, toluene and alcohol because they cause chemical damage to the PS.

(7) Wipe off saliva or water drops as soon as possible. Their long time contact with PS causes deformations and color fading.

Product specification The data sheet contains final product specifications.

## Limiting values

Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

#### Application information

Where application information is given, it is advisory and dose not form part of the specification.

#### Product Environmental certification

ROHS

#### REMARK

All The specifications listed in this document are guaranteed for module only. Post-assembled operation or component(s) may impact module performance or cause unexpected effect or damage and therefore listed specifications is not warranted after any Post-assembled operation.

# 2.2 Reliability test

|    | TEST                                          | CONDITION                                                                                                              | METHOD                      | REMARK |

|----|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------|

| 1  | High-Temperature Operation                    | T=50 <sup>°</sup> C RH=30%RH,For<br>240Hr                                                                              | IEC 60 068-2-2Bb            |        |

| 2  | Low-Temperature Operation                     | $T = 0^{\circ}C$ for 240 hrs                                                                                           | IEC 60 068-2-2Ab            |        |

| 3  | High-Temperature Storage                      | T=70°C RH=40%RH For<br>240Hr<br>Test in white pattern                                                                  | IEC 60 068-2-2Bb            |        |

| 4  | Low-Temperature Storage                       | T = -25°C, for 240 hrs<br>Test in white pattern                                                                        | IEC 60 068-2-2Ab            |        |

| 5  | High Temperature, High-<br>Humidity Operation | T=40 °C,RH=90%RH,For<br>168Hr                                                                                          | IEC 60 068-2-3CA            |        |

| 6  | High Temperature, High-<br>Humidity Storage   | T=60 ℃, RH=80%RH, For<br>240Hr<br>Test in white pattern                                                                | IEC 60 068-2-3CA            |        |

| 7  | Temperature Cycle                             | -25 ℃ (30min)~70 ℃<br>(30min),100 Cycle<br>Test in white pattern                                                       | IEC 60 068-2-14NB           |        |

| 8  | Package Vibration                             | 10~500Hz Direction : X,Y,Z<br>Duration: 1hours in each<br>direction                                                    |                             |        |

| 9  | Package Drop Impact                           | Drop from height of 122 cm<br>on Concrete surface<br>Drop sequence:1 corner,<br>3edges,<br>6face<br>One drop for each. | Full packed for<br>shipment |        |

| 10 | UV exposure Resistance                        | 765 W/m²for 168hrs,40°C                                                                                                | IEC 60068-2-5 Sa            |        |

| 11 | Electrostatic discharge                       | Machine model:<br>+/-250V,0Ω,200pF                                                                                     | IEC61000-4-2                |        |

Actual EMC level to be measured on customer application.

Note1: Stay white pattern for storage and non-operation test.

Note2: Operation is black/white/red pattern , hold time is 150S.

Note3: The function, appearence, opticals should meet the requirements of the test before

and after the test. Note4 : Keep testing after 2 hours placing at 20 °C - 25 °C .

# **3. Electrical Characteristics**

## 3.1 ABSOLUTE MAXIMUM RATING

| Symbol | Parameter                   | Rating       | Unit |  |  |  |

|--------|-----------------------------|--------------|------|--|--|--|

| VCI    | Logic supply voltage        | -0.5 to +6.0 | V    |  |  |  |

| TOPR   | Operation temperature range | 0 to 50      | °C   |  |  |  |

| TSTG   | Storage temperature range   | -25 to 60    | °C   |  |  |  |

| -      | Humidity range              | 40~70        | %RH  |  |  |  |

## Table 3.1-1: Maximum Ratings

Note: Maximum ratings are those values beyond which damages to the device may occur. Functional operation should be restricted to the limits in the Electrical Characteristics chapter.

Note 3-1: Tstg is the transportation condition, the transport time is within 10 days for  $-25^{\circ}$ C ~0°C or 50°C ~60°C.

## 3.2 DC CHARACTERISTICS

The following specifications apply for: VSS=0V, VCI=3.3V, TOPR=25℃.

| Symbol  | Parameter               | Test         | Applicable pin  | Min.     | Тур. | Max.    | Unit |

|---------|-------------------------|--------------|-----------------|----------|------|---------|------|

| VCI     | VCI operation voltage   | -            | VCI             | 2.2      | 3    | 3.7     | V    |

| VIH     | High level input        | -            | SDA, SCL, CS#,  | 0.8VDDIO | -    | -       | V    |

| VIL     | Low level input voltage | -            | D/C#, RES#, BS1 | -        | -    | 0.2VDDI | V    |

| VOH     | High level output       | IOH = -100uA |                 | 0.9VDDIO | _    | -       | V    |

| VOL     | Low level output        | IOL = 100uA  | BUSY,           | -        | -    | 0.1VDDI | V    |

| Iupdate | Module operating        | -            | -               | -        | 4.5  | -       | mΑ   |

| Isleep  | Deep sleep mode         | VCI=3.3V     | -               | -        |      | 2       | uA   |

Table 3.2-1: DC Characteristics

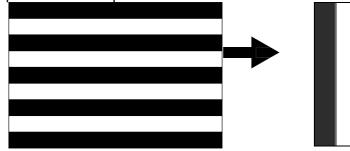

- The Typical power consumption is measured using associated 25°C waveform with following pattern transition: from horizontal scan pattern to vertical scan pattern. (Note 3-2)

- The listed electrical/optical characteristics are only guaranteed under the controller & waveform provided by Ingcool.

- Vcom value will be OTP before in factory or present on the label sticker.

Note 3-2

The Typical power consumption

# 3.3 Serial Peripheral Interface Timing

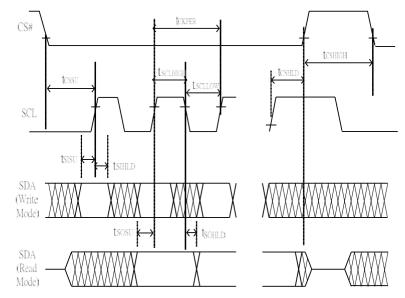

The following specifications apply for: VSS=0V, VCI=2.2V to 3.7V, TOPR=25°C

Write mode

| Symbol   | Parameter                                                                    | Min | ТурМа | x Unit |

|----------|------------------------------------------------------------------------------|-----|-------|--------|

| fSCL     | SCL frequency (Write Mode)                                                   |     | 20    | MHz    |

| tCSSU    | Time CS# has to be low before the first rising edge of SCLK                  | 20  |       | ns     |

| tCSHLD   | Time CS# has to remain low after the last falling edge of SCLK               | 20  |       | ns     |

| tCSHIGH  | Time CS# has to remain high between two transfers                            | 100 |       | ns     |

| tSCLHIGH | Part of the clock period where SCL has to remain high                        | 25  |       | ns     |

| tSCLLOW  | Part of the clock period where SCL has to remain low                         | 25  |       | ns     |

| tSISU    | Time SI (SDA Write Mode) has to be stable before the next rising edge of SCL | 10  |       | ns     |

| tSIHLD   | Time SI (SDA Write Mode) has to remain stable after the rising edge of SCL   | 40  |       | ns     |

## Read mode

| Symbol  | Parameter                                                                | Min | Тур | Max | Unit |

|---------|--------------------------------------------------------------------------|-----|-----|-----|------|

| fSCL    | SCL frequency (Read Mode)                                                |     |     | 2.5 | MHz  |

| tCSSU   | Time CS# has to be low before the first rising edge of SCLK              | 100 |     |     | ns   |

| tCSHLD  | Time CS# has to remain low after the last falling edge of SCLK           | 50  |     |     | ns   |

| tCSHIGH | Time CS# has to remain high between two transfers                        | 250 |     |     | ns   |

| tSCLHIG | Part of the clock period where SCL has to remain high                    | 180 |     |     | ns   |

| tSCLLOW | Part of the clock period where SCL has to remain low                     | 180 |     |     | ns   |

| tSOSU   | Time SO(SDA Read Mode) will be stable before the next rising edge of SCL |     | 50  |     | ns   |

| tSOHLD  | Time SO (SDA Read Mode) will remain stable after the falling edge of SCL |     | 0   |     | ns   |

Note: All timings are based on 20% to 80% of VDDIO-VSS

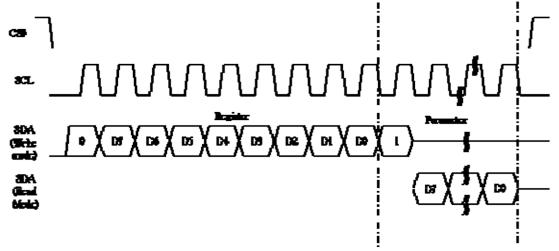

## Figure 3.3-1 : Serial peripheral interface characteristics

## 3.4 Power Consumption

| Parameter                             | Symbol | Conditions | TYP | Max | Unit | Remark |

|---------------------------------------|--------|------------|-----|-----|------|--------|

| Panel power consumption during update | -      | 25°C       | -   | 18  | mAs  | -      |

| Deep sleep mode                       | -      | 25°C       | -   | 2   | uA   | -      |

mAs=update average current  $\times$  update time

## 3.5 MCU Interface

#### 3.5-1) MCU interface selection

The 2.13inch e-Paper can support 3-wire/4-wire serial peripheral interface. In the Module, the MCU interface is pin selectable by BS1 pins shown in.

| Table 3.5-1: MCU Interface selection        |                                                        |  |  |  |

|---------------------------------------------|--------------------------------------------------------|--|--|--|

| BS1 MPU Interface                           |                                                        |  |  |  |

| L 4-lines serial peripheral interface (SPI) |                                                        |  |  |  |

| Н                                           | 3-lines serial peripheral interface (SPI) - 9 bits SPI |  |  |  |

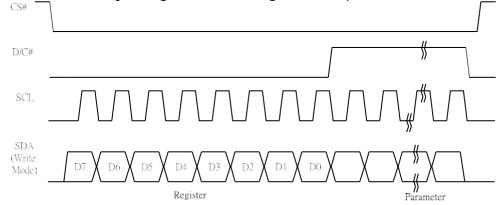

#### 3.5-2) MCU Serial Peripheral Interface (4-wire SPI)

The 4-wire SPI consists of serial clock SCL, serial data SDA, D/C# and CS#, The control pins status in 4-wire SPI in writing command/data is shown in Table 7- 2and the write procedure 4-wire SPI is shown in Figue 7-2.

Table 3.5-2 : Control pins status of 4-wire SPI

| Function   | SCL pin | SDA pin     | D/C# pin | CS# pin |

|------------|---------|-------------|----------|---------|

| Write      | 1       | Command bit | L        | L       |

| Write data | 1       | Data bit    | Н        | L       |

#### Note:

- (1) L is connected to VSS and H is connected to VDDIO

- (2) † stands for rising edge of signal

In the write mode, SDA is shifted into an 8-bit shift register on each rising edge of SCL in the order of D7, D6, ... D0. The level of D/C# should be kept over the whole byte. The data byte in the shift register is written to the Graphic Display Data RAM (RAM)/Data Byte register or command Byte register according to D/C# pin.

Figure 3.5-1: Write procedure in 4-wire SPI mode

In the Read mode:

- 1. After driving CS# to low, MCU need to define the register to be read.

- SDA is shifted into an 8-bit shift register on each rising edge of SCL in the order of D7, D6, ... D0 with D/C# keep low.

- 3. After SCL change to low for the last bit of register, D/C# need to drive to high.

- 4. SDA is shifted out an 8-bit data on each falling edge of SCL in the order of D7, D6, ... D0.

- 5. Depending on register type, more than 1 byte can be read out. After all byte are read, CS# need to drive to high to stop the read operation.

Figure v-2: Read procedure in 4-wire SPI mode

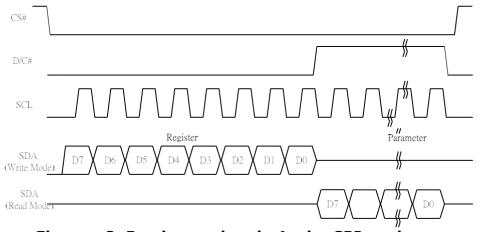

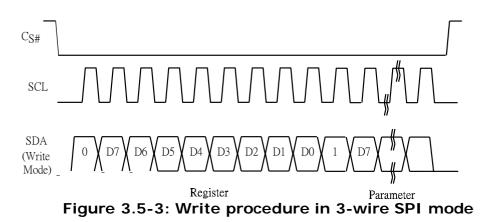

## 3.5-3) MCU Serial Peripheral Interface (3-wire SPI)

The 3-wire SPI consists of serial clock SCL, serial data SDA and CS#. The operation is similar to 4-wire SPI while D/C# pin is not used and it must be tied to LOW. The control pins status in 3-wire SPI is shown in Table 7-3.

| Function   | SCL pin | SDA pin     | D/C# pin | CS# pin |

|------------|---------|-------------|----------|---------|

| Write      | 1       | Command bit | Tie LOW  | L       |

| Write data | 1       | Data bit    | Tie LOW  | L       |

Table 3.5-3 : Control pins status of 3-wire SPI

#### Note:

(1)L is connected to VSS and H is connected to VDDIO

(2) stands for rising edge of signal

In the write operation, a 9-bit data will be shifted into the shift register on each clock rising edge. The bit shifting sequence is D/C# bit, D7 bit, D6 bit to D0 bit. The first bit is D/C# bit which determines the following byte is command or data. When D/C# bit is 0, the following byte is command. When D/C# bit is 1, the following byte is data. shows the write procedure in 3-wire SPI

In the Read mode:

- 1. After driving CS# to low, MCU need to define the register to be read.

- 2. D/C = 0 is shifted thru SDA with one rising edge of SCL

- 3. SDA is shifted into an 8-bit shift register on each rising edge of SCL in the order of D7, D6, ... D0.

- 4. D/C#=1 is shifted thru SDA with one rising edge of SCL

- 5. SDA is shifted out an 8-bit data on each falling edge of SCL in the order of D7, D6, ... D0.

- 6. Depending on register type, more than 1 byte can be read out. After all byte are read, CS# need to drive to high to stop the read operation.

Figure **3.5**-3: Read procedure in 3-wire SPI mode

## 3.6 Temperature sensor operation

Following is the way of how to sense the ambient temperature of the module. First, use an external temperature sensor to get the temperature value and converted it into HEX format with below mapping table, then send command 0x1A with the HEX temperature value to the module thru the SPI interface.

The temperature value to HEX conversion is as follow:

1. If the Temperature value MSByte bit D11 = 0, then

The temperature is positive and value (DegC) = + (Temperature value) / 16

2. If the Temperature value MSByte bit D11 = 1, then

The temperature is negative and value (DegC) =  $\sim$  (2's complement of Temperature value) / 16

| 12-bit binary<br>(2's complement) | Hexadecimal<br>Value | Decimal<br>Value | Value<br>[DegC] |

|-----------------------------------|----------------------|------------------|-----------------|

| 0111 1111 0000                    | 7F0                  | 2032             | 127             |

| 0111 1110 1110                    | 7EE                  | 2030             | 126.875         |

| 0111 1110 0010                    | 7E2                  | 2018             | 126.125         |

| 0111 1101 0000                    | 7D0                  | 2000             | 125             |

| 0001 1001 0000                    | 190                  | 400              | 25              |

| 0000 0000 0010                    | 002                  | 2                | 0.125           |

| 0000 0000 0000                    | 000                  | 0                | 0               |

| 1111 1111 1110                    | FFE                  | -2               | -0.125          |

| 1110 0111 0000                    | E70                  | -400             | -25             |

| 1100 1001 0010                    | C92                  | -878             | -54.875         |

| 1100 1001 0000                    | C90                  | -880             | -55             |

# 4. Typical Operating Sequence

## 4.1 Normal Operation Flow

## 5. COMMAND TABLE

| R/W# | D/C# | Hex | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Command | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------|------|-----|----|----|----|----|----|----|----|----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | 0    | 01  | 01 | 0  | 0  | 0  | 0  | 0  | 0  | 1  | Driver  | Gate setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0    | 1    |     | A7 | A6 | A5 | A4 | A3 | A2 | A1 | AO | Output  | A[8:0]= 127h [POR], 296 MUX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0    | 1    |     | 0  | 0  | 0  | 0  | 0  | 0  | 0  | A8 | control | MUX Gate lines setting as (A[8:0] + 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0    | 1    |     | 0  | 0  | 0  | 0  | 0  | B2 | B1 | BO |         | B[2:0] = 000 [POR].<br>B[2:0] = 000 [POR].<br>Gate scanning sequence and direction<br>B[2]: GD<br>Selects the 1st output Gate<br>GD=0 [POR],<br>G0 is the 1st gate output channel, gate<br>output sequence is G0,G1, G2, G3, .<br>GD=1,<br>G1 is the 1st gate output channel, gate<br>output sequence is G1, G0, G3, G2, .<br>B[1]: SM<br>Change scanning order of gate driver<br>SM=0 [POR],<br>G0, G1, G2, G3295 (left and right gate<br>interlaced)<br>SM=1,<br>G0, G2, G4G294, G1, G3,G295<br>B[0]: TB<br>TB = 0 [POR], scan from G0 to G295<br>TB = 1, scan from G295 to G0. |

|      |      |     |    |    |    |    |    |    |    |    |         | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0    | 0    | 03  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | Gate    | Set Gate driving voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0    | 1    |     | 0  | 0  | 0  | A4 | A3 | A2 | A1 | AO | Driving | A[4:0] = 00h [POR]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      |      |     |    |    |    |    |    |    |    |    | voltage | VGH setting from 12V to 20V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      |      |     |    |    |    |    |    |    |    |    | Control | A[4:0] VGH A[4:0] VGH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      |      |     |    |    |    |    |    |    |    |    |         | 07h 12 10h 16.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      |      |     |    |    |    |    |    |    |    |    |         | 08h 12.5 11h 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      |      |     |    |    |    |    |    |    |    |    |         | 09h 13 12h 17.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      |      |     |    |    |    |    |    |    |    |    |         | 0Ah 13.5 13h 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      |      |     |    |    |    |    |    |    |    |    |         | 0Bh 14 14h 18.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      |      |     |    |    |    |    |    |    |    |    |         | 0Ch 14.5 15h 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      |      |     |    |    |    |    |    |    |    |    |         | 0Dh 15 16h 19.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      |      |     |    |    |    |    |    |    |    |    |         | 0Eh 15.5 17h 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      |      |     |    |    |    |    |    |    |    |    |         | 0Fh 16 Other NA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <u>?/W#</u> |                     | Hex    | D7       | D6       | D5       | D4       | D3       | D2                  | D1       | DO       |        | Command    |           |     | Descript  | ion                    | [7 0]  |

|-------------|---------------------|--------|----------|----------|----------|----------|----------|---------------------|----------|----------|--------|------------|-----------|-----|-----------|------------------------|--------|

| 0           | 0                   | 04     | 0        | 0        | 0        | 0        | 0        | 1                   | 0        | (        | ~      | Source     |           |     |           | voltage A              |        |

| 0           | 1                   |        | A7<br>B7 | A6<br>B6 | A5<br>B5 | A4<br>B4 | A3<br>B3 | A2<br>B2            | A1<br>B1 | A0<br>B0 | — C    | Driving    |           |     |           | 0V B[7:0]<br>7:0] = 32 |        |

| 0           | 1                   |        | C7       | C6       | C5       | C4       | C3       | C2                  | C1       | CO       |        | /oltage    | [POR], \  |     |           | .0] = 52               |        |

| [_] (D]     |                     |        |          |          |          |          |          |                     |          |          | C      | Control    |           |     |           |                        |        |

|             | 7] = 1,<br>SH2 volt | 200 50 | tting    | from 2   | ) /\/ +/ |          |          | /B[7] =<br>1 /\/SLI |          | tago     | cotti  | ng from 9\ | / to 17\/ |     | ] = 0,    | rom 0 V                | to 17) |

| A/B[ 7      | VSH1/V              | SH A   | /B[7:    | VSH1     |          |          | v 311    | 1/ 0311             | 2 001    | laye     | settii | ng nom 4v  | 10 17 0   | VJL | setting i | 0111 - 7 V             | 10-170 |

| :0]         | 2                   | 0      |          | 2        |          |          | ۸/D[.    | 7 VSH1              | / ^      | /B[ 7    | VCL    | 1          |           |     | C[7:0]    | VSL                    | ]      |

| 8Eh         | 2.4                 | AI     | -h       | 5.7      |          |          | :0]      | VSH2                |          | 0]       | 1/V    |            |           |     | 1Ah       | -9                     | -      |

| 8Fh         | 2.5                 | B      | Dh       | 5.8      |          |          | _        |                     |          |          | H2     |            |           |     |           |                        | -      |

| 90h         | 2.6                 | B      | 1h       | 5.9      |          |          | 23h      | 9                   | 3        | Ch       | 14     |            |           |     | 1Ch       | -9.5                   |        |

| 91h         | 2.7                 | B      | 2h       | 6        |          |          | 24h      | 9.2                 | 3        | Dh       | 14.2   | 2          |           |     | 1Eh       | -10                    |        |

| 92h         | 2.8                 | B      | 3h       | 6.1      |          |          | 25h      | 9.4                 | 3        | Eh       | 14.4   | 4          |           |     | 20h       | -10.5                  |        |

| 93h         | 2.9                 | B      | 4h       | 6.2      |          |          | 26h      | 9.6                 | 3        | Fh       | 14.0   | 6          |           |     | 22h       | -11                    |        |

| 94h         | 3                   |        | 5h       | 6.3      |          |          | 27h      | 9.8                 | 4        | 0h       | 14.8   | 8          |           |     | 24h       | -11.5                  |        |

|             | 3.1                 |        | 5h       | 6.4      |          |          | 28h      | 10                  | 4        | 1h       | 15     |            |           |     | 26h       | -12                    |        |

| 95h         | 3.1                 |        |          | 6.5      |          |          | 29h      | 10.2                | 4        | 2h       | 15.2   | 2          |           |     | 28h       | -12.5                  |        |

| 96h         |                     |        | 7h       |          |          |          | 2Ah      | 10.4                |          | 3h       | 15.4   |            |           |     | 2Ah       | -13                    |        |

| 97h         | 3.3                 |        | 3h       | 6.6      |          |          | 2Bh      | 10.6                |          | 4h       | 15.0   |            |           |     | 2Ch       | -13.5                  | -      |

| 98h         | 3.4                 | B      | 9h       | 6.7      |          |          | 2Ch      | 10.8                |          | 5h       | 15.8   |            |           |     | 2Eh       | -14                    | -      |

| 99h         | 3.5                 | B      | ۹h       | 6.8      |          |          |          |                     |          |          | _      | 8          |           |     | 30h       | -14.5                  | -      |

| 9Ah         | 3.6                 | BI     | 3h       | 6.9      |          |          | 2Dh      | 11                  |          | 6h       | 16     |            |           |     |           |                        |        |

| 9Bh         | 3.7                 | B      | Ch       | 7        |          |          | 2Eh      | 11.2                |          | 7h       | 16.2   |            |           |     | 32h       | -15                    |        |

| 9Ch         | 3.8                 | BI     | Dh       | 7.1      |          |          | 2Fh      | 11.4                | 4        | 8h       | 16.4   | 4          |           |     | 34h       | -15.5                  |        |

| 9Dh         | 3.9                 | BI     | Eh       | 7.2      |          |          | 30h      | 11.6                | 4        | 9h       | 16.0   | 6          |           |     | 36h       | -16                    |        |

| 9Eh         | 4                   |        | -h       | 7.3      |          |          | 31h      | 11.8                | 4        | Ah       | 16.8   | 8          |           |     | 38h       | -16.5                  |        |

| 9Fh         | 4.1                 |        | Dh       | 7.4      |          |          | 32h      | 12                  | 4        | Bh       | 17     |            |           |     | 3Ah       | -17                    |        |

| A0h         | 4.2                 |        | 1h       | 7.5      |          |          | 33h      | 12.2                | C        | ther     | NA     |            |           |     | Other     | NA                     |        |

|             |                     |        |          |          |          |          | 34h      | 12.4                |          |          |        |            |           |     | I         | I                      | 1      |

| A1h         | 4.3                 |        | 2h       | 7.6      |          |          |          |                     |          |          |        |            |           |     |           |                        |        |

| A2h         | 4.4                 |        | 3h       | 7.7      |          |          | 35h      | 12.6                |          |          |        |            |           |     |           |                        |        |

| A3h         | 4.5                 | C4     | 4h       | 7.8      |          |          | 36h      | 12.8                |          |          |        |            |           |     |           |                        |        |

| A4h         | 4.6                 | C!     | ōh       | 7.9      |          |          | 37h      | 13                  |          |          |        |            |           |     |           |                        |        |

| A5h         | 4.7                 | Ce     | 5h       | 8        |          |          | 38h      | 13.2                |          |          |        |            |           |     |           |                        |        |

| A6h         | 4.8                 | C      | 7h       | 8.1      |          |          | 39h      | 13.4                |          |          |        |            |           |     |           |                        |        |

| A7h         | 4.9                 | C      | 3h       | 8.2      |          |          | 3Ah      | 13.6                |          |          |        |            |           |     |           |                        |        |

| A8h         | 5                   | C      | 9h       | 8.3      |          | -        | 3Bh      | 13.8                |          |          |        |            |           |     |           |                        |        |

| A9h         | 5.1                 | C      | ۹h       | 8.4      |          | _        | L        |                     |          |          |        | ]          |           |     |           |                        |        |

| AAh         | 5.2                 |        | 3h       | 8.5      |          | -        |          |                     |          |          |        |            |           |     |           |                        |        |

| ABh         | 5.3                 |        | Ch       | 8.6      |          | -        |          |                     |          |          |        |            |           |     |           |                        |        |

| ACh         | 5.4                 |        | Dh       | 8.7      |          | _        |          |                     |          |          |        |            |           |     |           |                        |        |

|             |                     |        |          |          |          | _        |          |                     |          |          |        |            |           |     |           |                        |        |

| ADh         | 5.5                 |        | Eh       | 8.8      |          | _        |          |                     |          |          |        |            |           |     |           |                        |        |

| AEh         | 5.6                 | 0      | ther     | NA       |          |          |          |                     |          |          |        |            |           |     |           |                        |        |

| R/W# | D/C# | Hex | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Command        | Description                                 |

|------|------|-----|----|----|----|----|----|----|----|----|----------------|---------------------------------------------|

| 0    | 0    | 08  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  |                | Program User Command Setting                |

|      |      |     |    |    |    |    |    |    |    |    |                | The command required CLKEN=1.               |

|      |      |     |    |    |    |    |    |    |    |    |                | Refer to Register 0x22 for detail.          |

|      |      |     |    |    |    |    |    |    |    |    |                | BUSY pad will output high during operation. |

|      |      |     |    |    |    |    |    |    |    |    |                |                                             |

|      |      |     |    |    |    |    |    |    |    |    | T              |                                             |

| 0    | 0    | 09  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 1  | Write Register | Write Register for User Command             |

| 0    | 1    |     | A7 | A6 | A5 | A4 | A3 | A2 | A1 | AO | for User       | Selection                                   |

| 0    | 1    |     | B7 | B6 | B5 | B4 | B3 | B2 | B1 | BO | Command        | A[7:0] ~ D[7:0]: Reserved                   |

| 0    | 1    |     | C7 | C6 | C5 | C4 | C3 | C2 | C1 | CO |                | Details refer to Application Notes of       |

| 0    | 1    |     | D7 | D6 | D5 | D4 | D3 | D2 | D1 | DO |                | User Command Setting                        |

|      |      |     |    |    |    |    |    |    |    |    |                |                                             |

| 0    | 0    | 0A  | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 0  | Read Register  | Read Register for User Command              |

|      |      |     |    |    |    |    |    |    |    |    | for User       |                                             |

|      |      |     |    |    |    |    |    |    |    |    | Command        |                                             |

|      |      |     |    |    |    |    |    |    |    |    |                |                                             |

| 0         0         0         0         1         1         0         0         Booster foot<br>and Phase 3 for sort start current and<br>duration start start current and<br>duration start current and<br>duration start current and<br>duration start start current and<br>duration start current and<br>duration start current and<br>duration start start current and<br>duration start current and<br>duration start start current and<br>duration start current and<br>duratin start curre | R/W# | D/C# | Hex | D7 | D6 | D5 | D4 | D3        | D2 | D1 | DO | Command      |                             | Description                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----|----|----|----|----|-----------|----|----|----|--------------|-----------------------------|------------------------------------------------------|

| 0         1         1         66         86         81         82         Control           0         1         0         66         C5         C4         C3         C2         C1         C0           0         1         0         0         D5         D4         D3         D2         D1         D0           0         1         0         0         D5         D4         D3         D2         D1         D0           0         1         0         0         D5         D4         D3         D2         D1         D0           0         1         0         0         D5         D4         D3         D2         D1         D0           0         1         0         0         D5         D4         D3         D2         D1         D0           0         1         0         0         D1         D2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0    | 0    |     | 0  | 0  | 0  | 0  | 1         | 1  | 0  | 0  | Booster Soft |                             | able with Phase 1, Phase 2                           |

| 0         1         1         C6         C5         C4         C3         C2         C1         C0           0         1         0         0         D5         D4         D3         D2         D1         D0           0         1         0         0         D5         D4         D3         D2         D1         D0           0         1         0         0         D5         D4         D3         D2         D1         D0           0         1         0         0         D5         D4         D3         D2         D1         D0           0         1         1         0         1         0         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |      |     |    |    | A5 |    | A3        |    |    |    |              |                             |                                                      |

| 0       1       0       0       D5       D4       D3       D2       D1       D0 <ul> <li>B(7.0) -&gt; Soft start satting for Phase -&gt; C(P(POR)</li> <li>C(7.0) -&gt; Soft start satting for Phase -&gt; C(P(POR)</li> <li>C(7.0) -&gt; Soft start satting for Phase -&gt; C(P(POR)</li> <li>C(7.0) -&gt; Soft start satting for Phase -&gt; C(P(POR)</li> <li>C(7.0) -&gt; Soft start satting for Phase -&gt; C(P(POR)</li> <li>C(7.0) -&gt; Soft start satting for Phase -&gt; C(P(POR)</li> <li>C(7.0) -&gt; Soft start satting for Phase -&gt; C(P(POR)</li> <li>C(7.0) -&gt; Soft start satting for Phase -&gt; C(P(POR)</li> <li>C(7.0) -&gt; Soft start satting for Phase -&gt; C(P(POR)</li> <li>C(7.0) -&gt; Soft start satting for Phase -&gt; C(P(POR)</li> <li>C(7.0) -&gt; Soft start satting for Phase -&gt; C(P(POR)</li> <li>C(7.0) -&gt; Soft start satting for Phase -&gt; C(P(POR)</li> <li>C(7.0) -&gt; Soft start satting for Phase -&gt; C(P(POR)</li> <li>C(7.0) -&gt; Soft start satting for Phase -&gt; C(P(POR)</li> <li>C(7.0) -&gt; Soft start satting for Phase -&gt; C(P(POR)</li> <li>C(7.0) -&gt; Soft start satting for Phase -&gt; C(P(POR)</li> <li>C(7.0) -&gt; Soft start satting for Phase -&gt; C(P(POR)</li> <li>C(7.0) -&gt; C(7.0) -&gt; C(7.0</li></ul>                                                                                                                                                                          |      |      |     |    |    |    |    | <u>сз</u> |    |    |    | CONTROL      | A[7:0] -> 9                 | for start setting for Phase1                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |      |     |    |    | D5 | D4 |           |    |    |    | 1            |                             | = 8Bh [POR]                                          |

| C17.0] - S oft start setting for Phase         - 6 06 (POR)         D17.0] -> Duration setting         D17.0] -> Duration setting         Bit Description of each byte:         ML6.01 / BL6.01 / C16.01.         Bit (6.4)         D10         3         011         4         100         5         101         6         101         6         101         6         010         3         011         4         100         5         101         6         010         3         011         4         100         5         101         6         0101         32         0110         33         0101         32         0110         33         0101         32         0111         4         1000         5.4         1011 <t< td=""><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td>B[7:0] -&gt; S</td><td>oft start setting for Phase2</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |      |     |    |    |    |    |           |    |    |    |              | B[7:0] -> S                 | oft start setting for Phase2                         |

| = 9 % I [POR]         D[7:0] -> Duration setting         = 0'h [POR]         Bit Description of each byte:         Alc:0] / B[6:0] / C[6:0]:         Bit(5:4]         D'(Veakest)         000         100         3         101         4         100         5         101         6         110         7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |      |     |    |    |    |    |           |    |    |    |              | $C[7\cdot 0] \rightarrow S$ |                                                      |

| - orh [Po8]           Bit Description of each byte:           AL:0.7 / BIs:01 / CI6:01:           Bit(6:4)         Driving Strength           Selecti         000           001         2           010         3           011         4           100         5           101         6           110         7           Bit(3:0)         Min Off Time Setting of GDR [Time unit]           0000:001         NA           100         2.6           0101         3.2           0101         3.2           0101         3.2           0101         3.2           0101         3.2           0101         3.2           0101         3.2           0101         3.2           0101         3.2           0101         3.2           0101         3.2           0101         3.2           0101         3.2           0101         3.2           0101         3.4           1001         7.3           1001         1.5           1101         1.8           1101<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |      |     |    |    |    |    |           |    |    |    |              | 0[7:0] > 0                  |                                                      |

| Bit Description of each tyte:         AI: 01 / Bit(5:4)       Driving Strength         000       1(Weakest)         001       2         010       3         011       4         100       5         101       6         100       5         101       6         100       5         101       6         100       2         010       3         101       6         100       5         101       6         100       2         0000       2.6         0101       3.9         0101       3.9         0101       3.9         0101       3.9         0101       3.9         0101       3.9         0101       3.9         0101       3.4         1000       5.4         1001       1.5         1010       1.8         1011       1.4         1000       9.8         1001       1.8         1010       1.8         1011       1.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |      |     |    |    |    |    |           |    |    |    |              | D[7:0] -> D                 |                                                      |

| Alf-c:01 / Zff-c:01 / Zff-c:01           Bit[6:4]         Diving Strength           Selecti         000           000         1 (Weakest)           001         2           010         3           011         4           100         5           101         6           110         7           Bit[3:0]         Min Off Time Setting of<br>GDR [Time unit]           0000         2.6           0101         3.2           0101         3.2           0101         3.2           0101         3.9           0111         4.6           1000         2.6           0101         3.2           0101         3.2           0101         3.2           0101         3.2           0101         3.9           0111         4.6           1000         5.4           1001         1.5           1101         1.5           1101         1.5           1101         1.5           1101         1.5           1101         1.5           1101         1.5 <tr< td=""><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td>Bit Descript</td><td></td></tr<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |      |     |    |    |    |    |           |    |    |    |              | Bit Descript                |                                                      |

| Selecti           000         1(Weakest)           001         2           010         3           011         4           100         5           101         6           110         7           Bit(30)         Min Off Time Setting of<br>GDR [ Time unit]           0000-001         NA           0100         2.6           0101         3.9           0111         4.6           1000         5.4           1000         5.4           1001         6.3           1010         7.3           1010         15.4           1010         15.4           1010         15.8           1111         16.5           1101         11.5           1110         13.8           1111         16.5           1101         13.8           1111         16.5           1111         16.5           1111         16.5           1111         16.5           1111         16.5           1111         16.5           1111         16.5           1111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |      |     |    |    |    |    |           |    |    |    |              | A[6:0] / B[0                | 6:0] / C[6:0]:                                       |